| EEL

6323 |

|

|

|

Selecting the correct technology library at the beginning of a project is important. It defines the model parameters that will be associated with the devices you use in your schematics and will lay the ground rules for what layers are available for your layouts. Trying to re-attach your library to a different technology partway through a project is possible, but can lead to unexpected results and/or lost development time. This page identifies a few technologies that have been tested and verified to work with our setup at UF, along with any special instructions required for their usage. A summary of the technologies is available at the bottom.

HP 0.60u AMOS14TB

| This technology is a 0.60-micron, 3.3V CMOS n-well process containing 3 metal layers and 1 poly layer. Additional information on the technology is available from MOSIS here. | |

It can be selected by choosing HP 0.60u

AMOS14TB (3M, sblock, thin-ox cap) from the tech library drop-down

list when creating a library. | |

| The simulator SpectreS must be used with this technology. | |

| There is full support for this process in our Cadence installation. No additional setup instructions should be necessary to use this technology for any part of the design process. |

TSMC 0.40u CMOS035

| This technology is a 0.40-micron, 3.3V CMOS n-well process containing 4 metal layers and 2 poly layers. Additional information on the technology is available from MOSIS here (refer to the information for the TSMC35_P2 technology). | |

It can be selected by choosing TSMC 0.40u

CMOS035 (4M, 2P, HV FET) from the tech library drop-down list when

creating a library. | |

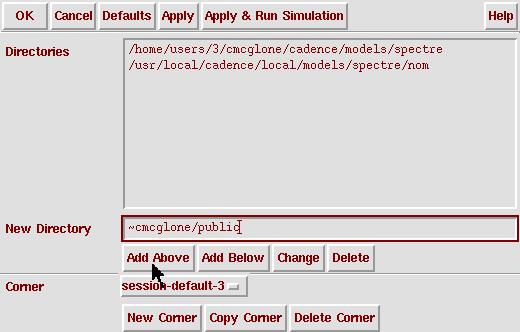

The simulator SpectreS must be used with this

technology. The model files required for the NMOS/PMOS transistors are

not part of our native Cadence setup. Instead, the model directory must be

explicitly identified when running simulations. After selecting SpectreS

within the Analog Environment window, goto Setup->Model Libraries,

enter the path to the model directory in the text box and click Add

Above. Be sure to click Apply and then OK

to accept the changes. The model directory is

available on the system at ~cmcglone/public.

You can reference it directly from there (easiest way, shown below), or copy

the model files (tsmc35N.m and tsmc35P.m) to your own directory structure and reference

them locally (still easy, but

you will not inherit changes if/when the original files are updated). Alternatively, you can download

the files here (NMOS model, PMOS

model) and copy them over to your UNIX

account manually (hardest way). |

|

The remaining portions of the design process (schematic entry, layout, DRC, extraction, and LVS) are fully supported by our Cadence installation for this technology. No additional setup instructions should be necessary. |

TSMC 0.24u CMOS025/DEEP

| This technology is a 0.24-micron, 2.5V CMOS n-well process containing 5 metal layers and 1 poly layer. Additional information on the technology is available from MOSIS here. | |

It can be selected by choosing TSMC 0.24u

CMOS025/DEEP (5M, HV FET) from the tech library drop-down list when

creating a library. | |

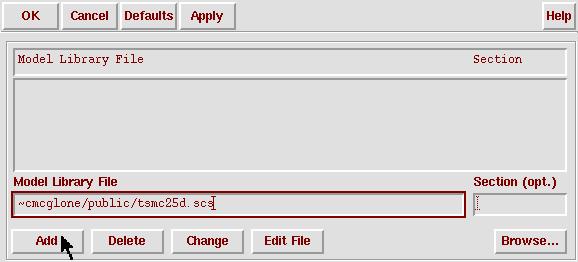

The simulator Spectre must be used with this

technology. The model file required for the NMOS/PMOS transistors is

not part of our Cadence setup. Instead, the model file must be

explicitly identified when running simulations. After selecting Spectre

within the Analog Environment window, goto Setup->Model Libraries,

enter the path to the model file in the text box and click Add

(leave the Section box empty). The model file is

available on the system under ~cmcglone/public/tsmc25d.scs.

You can reference it directly from there (easiest way, shown below), or copy

it to your own directory structure and reference it locally (still easy, but

you will not inherit changes if/when the original file is updated).

You can click Browse to locate the file, if necessary, from

within the Model Library Setup window. Alternatively, you can download

the file here and copy it over to your UNIX

account manually (hardest way). |

|

The remaining portions of the design process (schematic entry, layout, DRC, extraction, and LVS) are fully supported by our Cadence installation for this technology. No additional setup instructions should be necessary. |

TSMC 0.18u CMOS018/DEEP

| This technology is a 0.18-micron, 1.8V CMOS n-well process containing 6 metal layers and 1 poly layer. Additional information on the technology is available from MOSIS here. | |

It can be selected by choosing TSMC 0.18u

CMOS018/DEEP (6M, HV FET, sblock) from the tech library drop-down

list when creating a library. | |

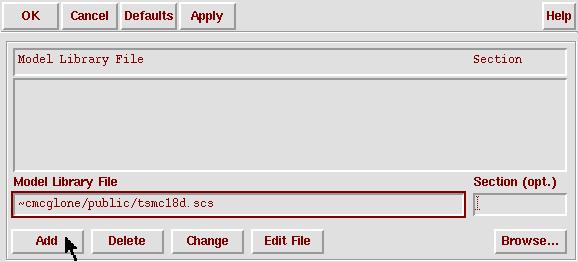

The simulator Spectre must be used with this

technology. The model file required for the NMOS/PMOS transistors is

not part of our Cadence setup. Instead, the model file must be

explicitly identified when running simulations. After selecting Spectre

within the Analog Environment window, goto Setup->Model Libraries,

enter the path to the model file in the text box and click Add

(leave the Section box empty). The model file is

available on the system under ~cmcglone/public/tsmc18d.scs.

You can reference it directly from there (easiest way, shown below), or copy

it to your own directory structure and reference it locally (still easy, but

you will not inherit changes if/when the original file is updated).

You can click Browse to locate the file, if necessary, from

within the Model Library Setup window. Alternatively, you can download

the file here and copy it over to your UNIX

account manually (hardest way). |

|

The remaining portions of the design process (schematic entry, layout, DRC, extraction, and LVS) are fully supported by our Cadence installation for this technology. No additional setup instructions should be necessary. |

Summary

| Process | GENERAL | SIMULATION | LAYOUT | |||||||

| Feature Size (um) |

Supply Voltage (V) |

Metal Layers |

Well Type |

Simulator | Model File* |

Lambda (um) |

Minor Grid Spacing** (um) |

Major Grid Spacing** (um) |

Design Rules |

|

| AMOS14TB | 0.60 | 3.3 | 3 | n | SpectreS | N/A | 0.30 | 0.15 | 0.75 | SCN3M_SUBM |

| CMOS035 (2P) | 0.40 | 3.3 | 4 | n | SpectreS | tsmc35N.m |

0.20 | 0.10 | 0.50 | SCN4ME_SUBM |

| CMOS025/DEEP | 0.24 | 2.5 | 5 | n | Spectre | tsmc25d.scs |

0.12 | 0.06 | 0.30 | SCN5M_DEEP |

| CMOS018/DEEP | 0.18 | 1.8 | 6 | n | Spectre | tsmc18d.scs |

0.09 | 0.045 | 0.225 | SCN6M_DEEP |

**Grid spacings are just recommendations; other values are possible.