NARC is a project commissioned by Dr. Alan George and the High Performance Computing and Simulation Research Lab at the University of Florida. The area of reconfigurable computing is a hot topic of interest to many clients, including the NSA and Department of Defense.

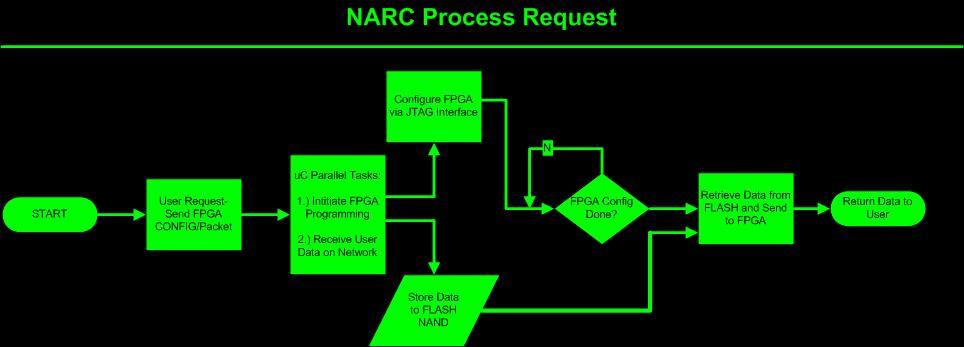

By using a Xilinx FPGA and a host microcontroller (uC), NARC can be sent network based function requests and is capable of performing any task that it is encoded to do. For example, the user might request a simple "+1 operation" wherein NARC is asked to take a stream of information and discretely increment each member by one. NARC is also capable of more difficult tasks such as an FFT operation or anything that can be built in VHDL and implemented on the FPGA.

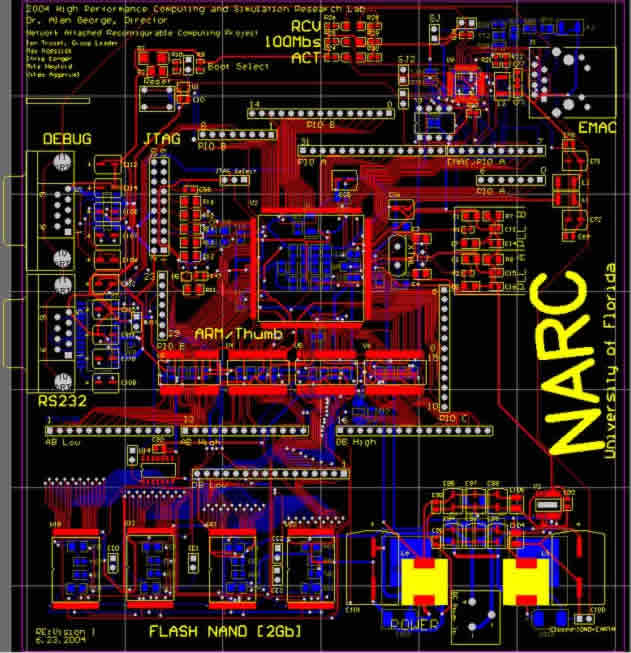

The microcontroller's duties include Ethernet MAC layers, memory control, RS232 communication, and data bus arbitration. The microcontroller chosen is the ARM920T ARM/Thumb based ATMEL AT91RM9200. This particular uC contains all of these features on chip except the ethernet PHY layer. It also includes a 32 bit data bus for communicating with the FPGA. The uC will be responsible for retrieving/storage of data from the network and handling any FPGA programming protocols. Data will be stored in 2Gb of FLASH NAND.

[click on image to enlarge]

The first prototype of NARC will be interfaced to a XILINX development board. It is also a two layer PCB. Two layer was chosen to minimize cost during design verification. Subsequent versions will be multilayer.

[click on image to enlarge]